Robot vacuums, a major household appliance that make life easier, are convenient but they often stumble on door thresholds that are not even very high. A similar threshold voltage exists in a transistor through which current flows. As long as the voltage exceeds the threshold voltage, the output impedance of the transistor is sharply lowered and current flows easily, improving its performance.

Credit: POSTECH

Robot vacuums, a major household appliance that make life easier, are convenient but they often stumble on door thresholds that are not even very high. A similar threshold voltage exists in a transistor through which current flows. As long as the voltage exceeds the threshold voltage, the output impedance of the transistor is sharply lowered and current flows easily, improving its performance.

Recently, a POSTECH research team led by Professor Yong-Young Noh and Ph.D. candidates Huihui Zhu and Ao Liu (Department of Chemical Engineering), in collaboration with Samsung Display, has developed a p-channel perovskite thin film transistor (TFT) with a threshold voltage of 0 V.

Despite the impressive development of metal halide perovskites in diverse optoelectronics, progress on high-performance transistors employing state-of-the-art perovskite channels has been limited due to ion migration and large organic spacer isolation

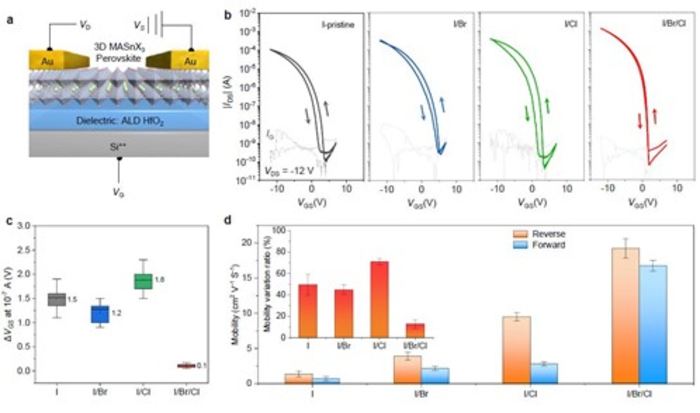

In this study, the research team constructed a methylammonium-tin-iodine (MASnI3) semiconductor layer by mixing the halide anions (iodine-bromine-chlorine) to increase the stability of the transistor. The device made using this semiconductor layer showed high performance and excellent stability without hysteresis.

In experiments, the TFTs realized a high hole mobility of 20cm2V-1s-1 and 10 million on/off current ratio, and also reached the threshold voltage of 0 V. A P-channel perovskite transistor with a threshold voltage of 0 V is the first such case in the world. By making the material into a solution, the researchers also enabled the transistors to be printed, lowering their manufacturing cost.

Through this study, the research team demonstrated that the primary cause of the hysteresis that lowers the performance of the perovskite TFTs is the minority carrier trapping, not the ion migration. By lowering the threshold voltage, the movement of electrons and holes is undisturbed, enabling the current to flow smoothly.

Furthermore, the research team succeeded in integrating the perovskite TFTs with commercialized n-channel6 indium gallium zinc oxide (IGZO) TFTs on a single chip to construct high-gain complementary inverters through a circuit-printing method.

This study is drawing attention from academic circles as a technology applicable to the development of OLED display driving circuits, P-channel transistors of vertically stacked devices, and neuromorphic computing for AI calculations.

Recently published in Nature Communications, this study was conducted with the support from the Mid-Career Researcher Program of the National Research Foundation of Korea, and from the Samsung Display Corporation. The POSTECH research team and Samsung Display have already applied for domestic and international patents for this technology last year.

Journal

Nature Communications

DOI

10.1038/s41467-022-29434-x

Article Title

High-performance hysteresis-free perovskite transistors through anion engineering

Article Publication Date

1-Apr-2022