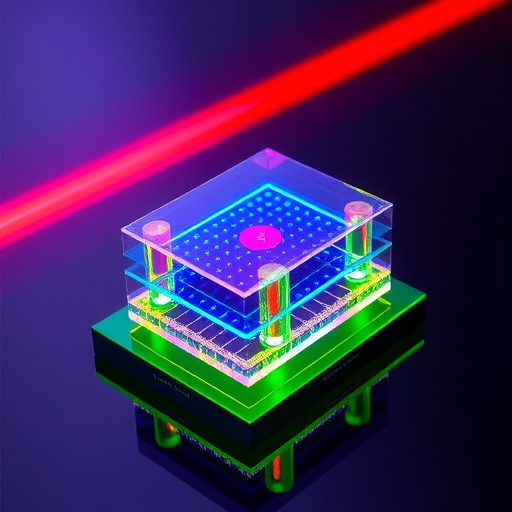

In a groundbreaking advancement in photonics, researchers have unveiled a novel method for creating monolithic III–V membrane photonic crystal lasers directly on silicon-on-insulator (SOI) platforms through a process known as selective lateral heteroepitaxy. This pioneering technique not only addresses longstanding integration challenges of III–V semiconductor materials with mature silicon technology but also heralds a new era of compact, high-performance lasers vital for the future of optical communication and on-chip photonic circuits.

The core innovation revolves around the growth of III–V compound semiconductors, which are renowned for their superior direct bandgap and exceptional optoelectronic properties, on SOI wafers. SOI substrates, celebrated for their optical confinement and low-loss characteristics, have struggled to seamlessly incorporate efficient laser sources due to the inherent crystal lattice mismatch and thermal expansion differences between silicon and III–V materials. The researchers’ method of selective lateral heteroepitaxy dexterously navigates these issues, enabling high-quality crystalline membranes to form with minimal defects.

At the heart of this technique lies a carefully engineered lateral growth approach. Instead of growing the III–V material vertically on silicon, which typically results in threading dislocations and wafer bowing, the team initiates growth from patterned nucleation sites on the SOI, enabling the III–V material to extend laterally over the oxide layer. This lateral expansion effectively reduces strain accumulation and promotes the formation of defect-free membranes that are just a few hundred nanometers thick, perfectly suited for integration with photonic crystal structures.

Photonic crystals, the nanostructured optical materials that control light propagation through periodic modulation of the refractive index, offer unparalleled control over photonic modes and emission characteristics. By incorporating photonic crystal cavities into the III–V membrane lasers, the researchers have optimized the feedback mechanisms required for lasing. This leads to ultracompact devices with high-quality (Q) factors, enabling lasers to operate at exceptionally low thresholds and with enhanced spectral purity.

One of the most compelling outcomes of this research is the demonstration of coherent laser emission directly on the SOI platform without the need for complex wafer bonding or flip-chip processes, which have hitherto been the industry standard. The monolithic integration ensures superior thermal management, smaller footprints, and scalability, paving the way for mass production of photonic integrated circuits (PICs) with integrated active laser sources.

Furthermore, the utilization of selective lateral heteroepitaxy facilitates precise control over the composition and thickness of the III–V layers. This degree of control directly influences the emission wavelength and modal characteristics of the lasers, enabling customized devices spanning key telecommunications wavelengths. It also opens avenues for multifunctional devices where active gain regions can be selectively positioned adjacent to passive waveguides, dramatically boosting photonic circuit complexity and functionality.

The research team meticulously analyzed the crystalline quality and optical performance of the fabricated devices. High-resolution transmission electron microscopy revealed atomically sharp interfaces free from extended defects, while photoluminescence and electroluminescence characterizations confirmed robust optical gain and lasing action. The devices exhibited threshold currents significantly lower than conventional counterparts, underscoring the efficiency gains from this fabrication strategy.

This technological breakthrough has ripple effects across multiple domains. High-density photonic integration on SOI is a linchpin for developing next-generation data centers, where energy-efficient, high-speed optical interconnects are critical. The demonstrated lasers could enable on-chip optical interconnects with unprecedented performance metrics, drastically reducing the energy per bit and alleviating the bandwidth bottlenecks plaguing modern electronics.

From a scientific standpoint, the ability to achieve defect-minimized III–V membranes on silicon augments the fundamental understanding of lattice mismatched epitaxy and strain relaxation. It lends insights into strain-driven crystal growth mechanisms and defect propagation control, enriching the materials science community’s toolbox for heterointegration of dissimilar semiconductors.

Moreover, this approach holds promise for the burgeoning field of quantum photonics, where integration density and photon coherence are crucial. The compatibility with existing silicon photonics platforms means that single-photon sources, entangled photon pair generators, and other quantum light emitters could be monolithically integrated with passive circuitry, simplifying device architectures and enhancing stability.

Looking forward, the scalability of the selective lateral heteroepitaxy technique suggests its applicability beyond lasers. Optical modulators, detectors, and nonlinear optical elements could be fabricated concurrently on a single chip, facilitating the construction of complete photonic systems-on-chip optimized for various applications spanning sensors, communications, and computing.

While challenges remain, such as further refinement of growth uniformity over large wafer areas and integration with complementary metal-oxide-semiconductor (CMOS) electronics, the current research represents a critical step toward industrial deployment. The seamless integration of efficient light sources on silicon furnishes the photonics community with a powerful platform to explore novel device concepts and improve existing technologies.

In essence, the reported monolithic III–V membrane photonic crystal lasers exemplify the synergy between advanced materials engineering and nanophotonic design. By leveraging selective lateral heteroepitaxy on SOI substrates, the research paves the way for dense, low-power, high-speed optical circuits that could fundamentally transform the landscape of data processing and communication.

This innovation aligns perfectly with the increasing demand for miniaturized, integrated photonic solutions capable of meeting the insatiable appetite for data throughput and energy efficiency. The potential applications are vast, from inter-chip optical links to on-chip sensors and beyond, positioning this technology as a cornerstone in the ongoing photonic revolution.

Ultimately, the successful demonstration of these monolithic lasers affirms the feasibility of marrying III–V optoelectronic materials with silicon’s scalability, combining the best attributes of both worlds. This heralds a future where integrated photonic circuits are not just experimental prototypes but everyday components driving the next wave of technological progress.

The research detailed here was meticulously documented and can be found in the article titled “Monolithic III–V membrane photonic crystal lasers on SOI using selective lateral heteroepitaxy,” published in the journal Light: Science & Applications in January 2026.

Subject of Research: Monolithic integration of III–V membrane photonic crystal lasers on silicon-on-insulator substrates using selective lateral heteroepitaxy.

Article Title: Monolithic III–V membrane photonic crystal lasers on SOI using selective lateral heteroepitaxy.

Article References:

Zeng, C., Ren, Z., Lei, Z. et al. Monolithic III–V membrane photonic crystal lasers on SOI using selective lateral heteroepitaxy. Light Sci Appl 15, 98 (2026). https://doi.org/10.1038/s41377-025-02074-8

Image Credits: AI Generated

DOI: 30 January 2026

Tags: crystal lattice mismatch solutionsengineered lateral growth approachhigh-performance laser sourcesIII-V compound semiconductorsintegration of III-V semiconductorslow-loss photonic devicesmonolithic III-V photonic crystal laserson-chip photonic circuitsoptical communication advancementsoptical confinement in SOIselective lateral heteroepitaxy techniquesilicon-on-insulator platform